Advancing Verilog Generation with LLMs

A hierarchical dataset approach to improve hardware design coding

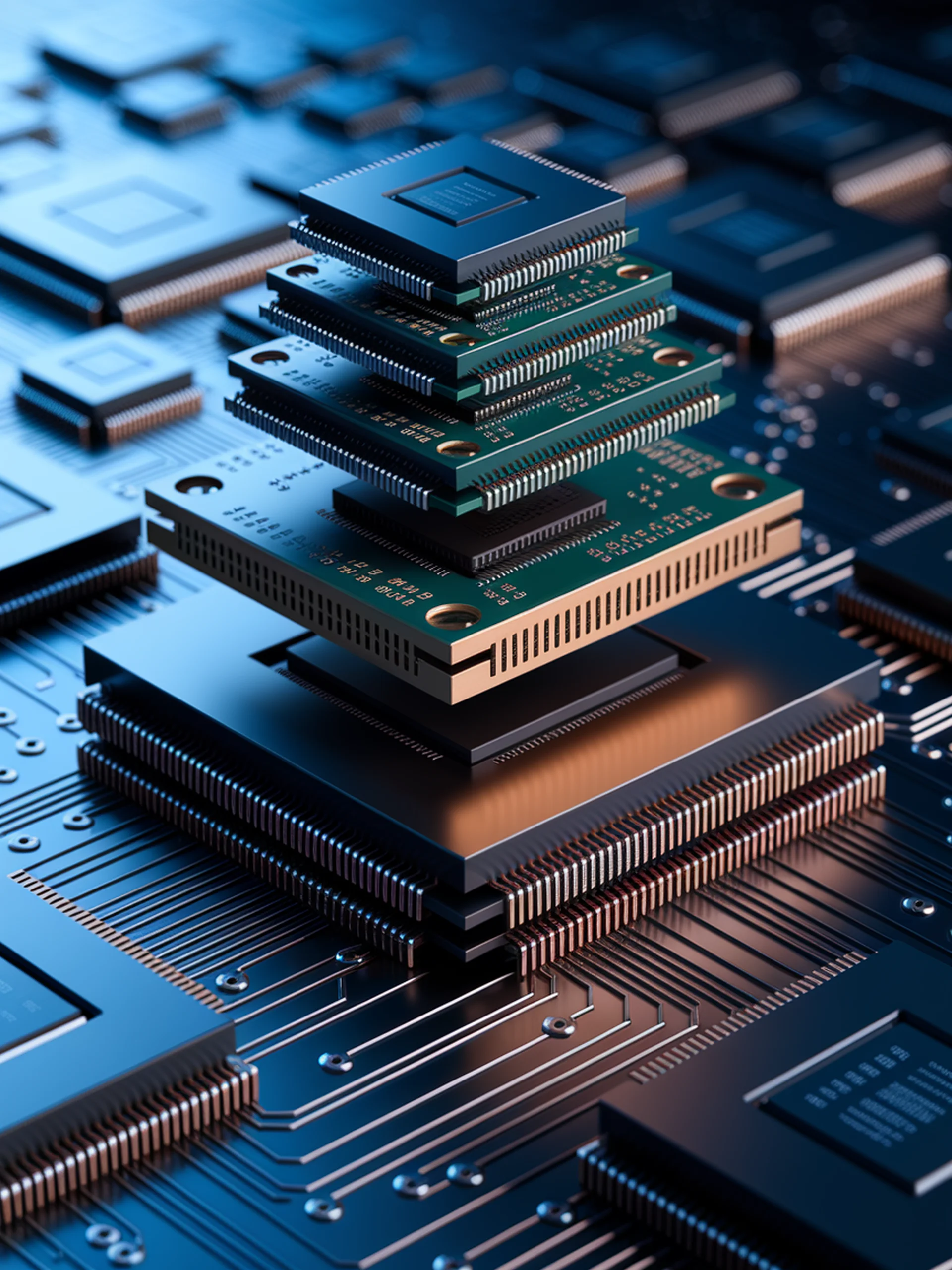

PyraNet introduces a multi-layered dataset specifically designed to enhance large language models' ability to generate high-quality Verilog code for hardware design.

- Creates a structured, hierarchical dataset of Verilog code samples

- Addresses the critical gap in specialized training resources for hardware description languages

- Implements novel fine-tuning techniques tailored for Verilog code generation

- Enables more reliable automated hardware design through improved code quality

This research is significant for hardware engineering as it brings AI-assisted design tools closer to practical implementation, potentially accelerating development cycles and reducing design errors in complex hardware systems.